<sup>1</sup> Arm systems semantics

2

3

4

5

6

7

8

Ben Simner University of Cambridge

This thesis is submitted for the degree of Doctor of Philosophy Department of Computer Science and Technology Wolfson College, Cambridge

January 10, 2025

### <sup>,</sup> Preface

<sup>10</sup> This dissertation is the result of my own work and includes nothing which is the outcome of work done in <sup>11</sup> collaboration except where specifically indicated in the text.

<sup>12</sup> It is not substantially the same as any work that has already been submitted, or, is being concurrently <sup>13</sup> submitted, for any degree, diploma or other qualification at the University of Cambridge or any other

<sup>13</sup> submitted, for any degree, diploma or other qualification at the University of Cambridge or any

<sup>14</sup> University or similar institution except as declared in the preface and specified in the text.

<sup>15</sup> It does not exceed the prescribed word limit for the relevant Degree Committee.

16 This dissertation contains:

$_{\rm 17}$   $\,\,\triangleright\,\,64144$  total words as counted by detex | wc -w

$_{\tt 18}$   $\triangleright$  60005+864+1475 (304/85/181/17) Total (errors:1) words as counted by texcount

### <sup>19</sup> Abstract

20 Computing relies on architecture specifications to decouple hardware and software development. Historically

<sup>21</sup> these have been prose documents, with all the problems that entails, but research over the last ten years has

22 developed rigorous and executable-as-test-oracle specifications of mainstream architecture instruction sets

$_{23}$  and 'user-mode' concurrency, clarifying architectures and bringing them into the scope of programming-

24 language semantics and verification.

<sup>25</sup> However, the *system semantics*, of address translation and TLB maintenance, instruction-fetch and its

<sup>26</sup> required cache maintenance, and exceptions and interrupts, remains mostly obscure, leaving us without a

27 solid foundation for verification of security-critical systems software.

$_{28}$  We produce precise mathematical models, for those aspects of the Arm A-class architecture. We implement

<sup>29</sup> these models as executable models, in both microarchitectural-flavoured operational and declarative

<sup>30</sup> axiomatic style formats. We validate these models, against currently available hardware through the

production and evaluation of hardware test harnesses and test suites, and against the architectural intent through discussions with Arm architects. We produce a variety of hand-written and machine-generated

through discussions with Arm architects. We produce a variety of hand-written as litmus tests, exercising parts of the architecture previously unexplored.

We discuss the nature of producing such models, the challenges that writing specifications of existing systems entails, and briefly touch upon how these models have evolved over time, and how we imagine

they will evolve in the future as the remaining questions are resolved.

### A lay summary

for bjørnar

<sup>39</sup> Modern computing devices have become increasingly complex over time, powered by chips with many <sup>40</sup> interacting components: network controllers; audio and signal processing; graphics processing; memory <sup>41</sup> controllers; and at the heart is the central processing unit, or CPU. The CPU is the principle director of <sup>42</sup> the whole machine, in charge of running all the software and coordinating all the components together. It <sup>43</sup> is the CPU that does all the calculations, it directs data to be read or written, it manages connections <sup>44</sup> over the network, it receives all the input from the outside world and decides how to respond. In short, <sup>45</sup> the CPU is the brain of the computer.

<sup>46</sup> Historically, a computer was a box with some gears, presenting the user a selection of buttons for various

<sup>47</sup> mathematical calculations. As time progressed, computers moved from mechanical to electronic. They

<sup>48</sup> moved from manual to automated, not actioning operations as directed by a human but executing *programs*:

<sup>49</sup> pre-determined sequences of *instructions* telling the computer which set of operations to perform.

In the days of EDSAC, the instructions were few and simple, e.g.: read a number from the input tape, add 50 or subtract two numbers, load a number from memory, store a number into memory, go to a particular 51 instruction, display a number to the user, stop the machine and ring the bell. Computers have advanced 52 much since then, but the interface has not: we still program by giving the machine a sequence of very 53 simple instructions to perform. There are now many *instruction set architectures* (ISAs), each defining 54 standard collections of instructions. CPUs with Arm, x86 (Intel/AMD), Power (IBM), and RISC-V ISAs 55 now power billions of devices globally. These ISAs are far bigger than EDSAC's measly  $\sim 20$  instructions, 56 with the, comparatively small, Arm ISA defining 402 instructions in its base architecture alone. 57

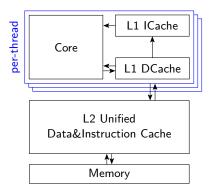

Modern CPUs have advanced in ways other than just having larger ISAs: caches are placed between the 58 CPU and memory, making data much quicker to access; they have become *multicore*, placing multiple 59 CPUs side-by-side on the same chip; and CPU designs have become superscalar, able to perform multiple 60 operations at the same time. The latter of these optimisations is possible because many instructions 61 require multiple steps to perform. For example, even a simple 'add two numbers' instruction requires 62 at least three steps: first to retrieve or load the input numbers from somewhere, before it is able to 63 actually calculate the sum, finally it must store the result somewhere. To implement these steps, CPUs 64 are distributed systems, composed of many smaller highly specialised units within them: small dedicated 65 circuits for adding numbers, accessing temporary data storage (registers), retrieving the next instruction 66 to execute, and so on. In the 1960's CPU designs gained a clever trick: they execute instructions in 67 a *pipeline*. Once an instruction is done with a particular unit, the next instruction can start using it 68 immediately, before the first has even completely finished. This is the essence of superscalar CPUs. 69

<sup>70</sup> Superscalar and multicore machines can have multiple instructions touching the same shared data <sup>71</sup> simultaneously, or in an order other than they appeared in the original sequence of instructions in the <sup>72</sup> program. If the programmer instructs two cores to concurrently access the same location, then the <sup>73</sup> behaviour of the machine is now determined not by the simple description of the individual instructions, <sup>74</sup> but by the complex interaction of these implementation-specific optimisations. Figuring out *what* can

<sup>75</sup> happen in that case is the field of *relaxed memory*. Or, what happens if the user pushes two buttons that

touch the same data at the same time? That is the object of study of this thesis.

$\pi$  In particular, we are interested in those buttons not for the every day programs, but those which give

<sub>78</sub> lower-level control of the machine. These are the instructions used by operating systems to manage

<sup>79</sup> many programs at once, and by hypervisors in the cloud to protect and isolate multiple customers virtual

machines from one another. To understand the behaviour of those instructions is critical in order to be able to produce robust software that uses them and to make credible claims about said software.

We do this in three steps. We (1) engage in broad technical discussions with architects and hardware 82 designers. We guide such discussions with specific software patterns or hardware optimisations in mind, 83 focusing on small representative experimental programs or *litmus tests*. We (2) reinforce the results of those 84 discussions through empirical analysis of existing hardware by building tools and using them to gather 85 experimental data, which further informs our and the architects' understanding. Finally, we (3) employ 86 the tools and techniques from programming language theory to build robust formal mathematical models 87 giving a clear definition to that interface. All this *clarifies* the architects' intent, gives software engineers 88 a sturdier basis to appeal to, and hopefully will enable richer efforts in certification and verification of 89

$_{90}$  those key pieces of software that we all rely on to perform correctly and to keep our data secure.

# **.** Contents

| 92  | 1 | Intr | roduction                             |

|-----|---|------|---------------------------------------|

| 93  |   | 1.1  | Arm-A architecture overview           |

| 94  |   | 1.2  | Systems software                      |

| 95  |   | 1.3  | Relaxed memory                        |

| 96  |   | 1.4  | Contributions                         |

| 97  |   |      | 1.4.1 Artifacts                       |

| 98  |   | 1.5  | Publications and collaborations       |

| 99  |   | 1.6  | Overview                              |

| 100 | 2 | Mod  | delling Arm: background               |

| 101 |   | 2.1  | Relaxed behaviours and litmus testing |

| 102 |   |      | 2.1.1 Thread-local ordering           |

| 103 |   |      | 2.1.2 Coherence                       |

| L04 |   |      | 2.1.3 Multi-copy atomicity            |

| L05 |   | 2.2  | Intra-instruction semantics           |

| L06 |   | 2.3  | Arm-A operational model               |

| L07 |   | 2.4  | Arm-A axiomatic model                 |

| 108 |   |      | 2.4.1 Arm-A candidate executions      |

| L09 |   |      | 2.4.2 Arm-A axioms                    |

| 110 |   | 2.5  | The isla-axiomatic tool               |

|     |   |      |                                       |

| 111 |   |      | 2.5.1 ISA/concurrency interface       |

## 113 I Instruction fetch

| 114 | 3 | Rela | axed instruction fetching                    | <b>40</b> |

|-----|---|------|----------------------------------------------|-----------|

| 115 |   | 3.1  | Introduction                                 | 41        |

| 116 |   | 3.2  | Industry practice and the existing Arm prose | 42        |

| 117 |   | 3.3  |                                              | 44        |

| 118 |   | 3.4  | Coherence                                    | 46        |

| 119 |   |      | 3.4.1 Instruction-to-Instruction coherence   | 46        |

| 120 |   |      | 3.4.2 Data-to-Instruction coherence          | 47        |

| 121 |   |      | 3.4.3 Instruction-to-Data coherence          | 48        |

| 122 |   | 3.5  | Cross-thread synchronisation                 | 49        |

| 123 |   | 3.6  | Cache maintenance                            | 50        |

| 124 |   |      | 3.6.1 Synchronisation on a single thread     | 50        |

| 125 |   |      | 3.6.2 Broadcast cache maintenance            | 51        |

| 126 |   | 3.7  | Dependencies                                 | 53        |

| 127 |   |      | 3.7.1 Address dependencies                   | 53        |

| 128 |   |      | 3.7.2 Control dependencies                   | 53        |

| 129 |   | 3.8  | Multi-Copy Atomicity                         | 54        |

| 130 |   | 3.9  | More on instruction caches                   | 54        |

| 131 |   | 3.10 | Points of Unification and Coherency          | 55        |

| 132 |   |      | 3.10.1 Late unification                      | 56        |

| 133 |   |      | 3.10.2 Promotion                             | 57        |

|     |   |      |                                              |           |

39

|            | E O                |       | Dependencies .<br>Reads-from |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

|------------|--------------------|-------|------------------------------|----------|---------------------------------------|-----------|-------|------|----|------|-----|-----|-----|-------|-----|-----|----|-----|-----------------|

| 165<br>166 | E 9                | 515   | eads-from .                  |          |                                       |           |       |      |    | <br> |     |     |     |       |     |     |    |     | 75              |

| 166        | E 63               |       |                              | rolation | <b>S</b>                              |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

|            | 5.2                |       | and auxiliary                |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 167        |                    |       | Arm ifetch even              |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 168        |                    |       | Cache mainten                |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 169        |                    |       | Coherence                    |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 170        |                    |       | Program order                |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 171        |                    |       | nstruction syn               |          |                                       | · · · · · |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 172        |                    |       | Data synchroni               |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 173        |                    |       | Data cache ma                |          | · · · · · · · · · · · · · · · · · · · | /         |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 174        |                    |       | Cache mainten                | -        |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 175        |                    | 5.2.9 | Constrained U                | npredict | table .                               |           |       | • •  |    | <br> | ••• | ••• | • • |       | • • | • • | •  |     | 79              |

| 176 6      | <b>Vali</b><br>6.1 |       | the ifetch mo                |          | e tho er                              | chitoc    | turol | into | nt |      |     |     |     |       |     |     |    |     | <b>80</b><br>80 |

| 177        |                    |       |                              | -        |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 178        | 6.2                | -     | ondence betwe                |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 179        |                    |       | Making the ope               |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 180        | 0.0                |       | Making the axi               |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 181        |                    |       | ence of the mo               |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 182        | 6.4                |       | ng against har               |          |                                       |           |       |      |    |      |     |     |     |       |     |     |    |     |                 |

| 183        |                    | 6.4.1 | Results from ha              | ardware  | e                                     |           |       |      |    | <br> |     |     |     |       | ••• |     | •• |     | 83              |

| 183        |                    | 6.4.1 | tesults from h               | ardware  | · · · · ·                             |           |       | • •  |    | <br> |     |     | ••• | <br>• |     | • • | •  | • • | 83              |

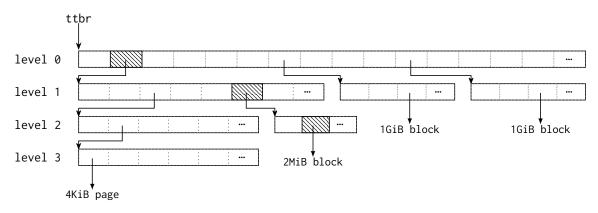

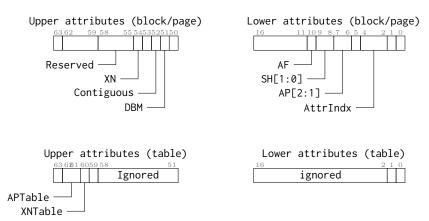

| 187 |   | 7.2  | Virtual Memory                                                                                                                               |

|-----|---|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 188 |   | 7.3  | Arm Translation Tables                                                                                                                       |

| 189 |   |      | 7.3.1 Translation table format                                                                                                               |

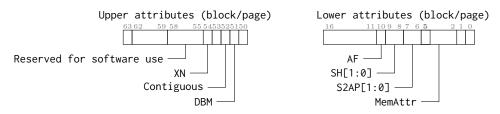

| 190 |   |      | 7.3.2 Attributes                                                                                                                             |

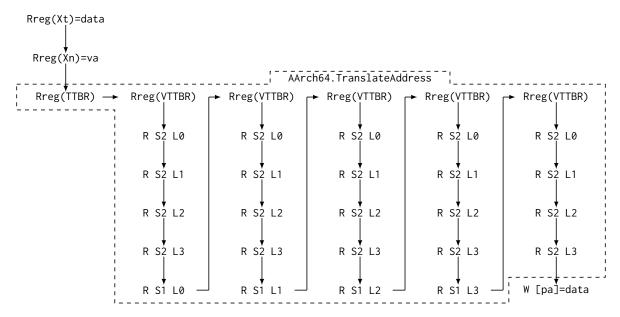

| 191 |   | 7.4  | The Arm translation table walk                                                                                                               |

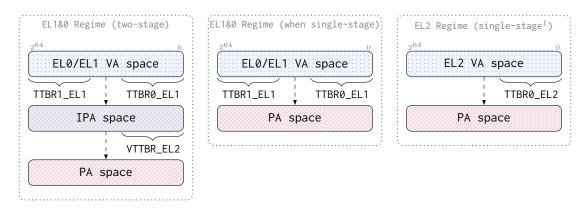

| 192 |   | 7.5  | Virtualisation                                                                                                                               |

| 193 |   | 7.6  | Translation regimes                                                                                                                          |

| 194 |   | 7.7  | Caching in TLBs                                                                                                                              |

|     |   |      |                                                                                                                                              |

| 195 | 8 | Rela | axed virtual memory 102                                                                                                                      |

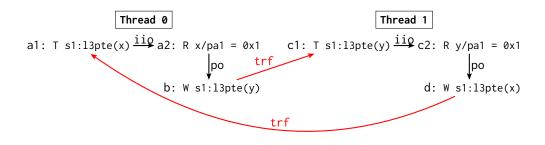

| 196 |   | 8.1  | Virtual memory litmus tests                                                                                                                  |

| 197 |   | 8.2  | Aliased data memory                                                                                                                          |

| 198 |   |      | 8.2.1 Virtual coherence                                                                                                                      |

| 199 |   |      | 8.2.2 Aliasing different locations                                                                                                           |

| 200 |   |      | 8.2.3 Might be same (physical) address                                                                                                       |

| 201 |   | 8.3  | What can be cached in TLBs 109                                                                                                               |

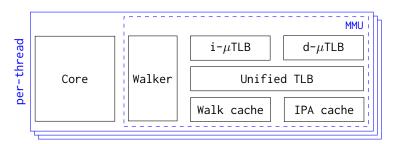

| 202 |   |      | 8.3.1 Microarchitectural TLBs                                                                                                                |

| 203 |   |      | 8.3.2 Model MMU                                                                                                                              |

| 204 |   |      | 8.3.3 Invalid entries                                                                                                                        |

| 205 |   | 8.4  | Reads not from TLB                                                                                                                           |

| 206 |   |      | 8.4.1 Out-of-order execution                                                                                                                 |

| 207 |   |      | 8.4.2 Enforcing thread-local ordering                                                                                                        |

| 208 |   |      | 8.4.3 Enhanced Translation Synchronization                                                                                                   |

| 209 |   |      | 8.4.4 Forwarding to the translation table walker                                                                                             |

| 210 |   |      | 8.4.5 Speculative execution                                                                                                                  |

| 211 |   |      | 8.4.6 Single-copy atomicity 122                                                                                                              |

| 212 |   |      | 8.4.7 Multi-copy atomicity                                                                                                                   |

| 213 |   |      | 8.4.8 Translation-table-walk intra-walk ordering                                                                                             |

| 214 |   |      | 8.4.9 Multiple translations within a single instruction                                                                                      |

| 215 |   | 8.5  | Caching of translations in TLBs                                                                                                              |

| 216 |   |      | 8.5.1 Cached translations                                                                                                                    |

| 217 |   |      | 8.5.2 TLB fills                                                                                                                              |

| 218 |   |      | 8.5.3 microTLBs                                                                                                                              |

| 219 |   |      | 8.5.4 Partial caching of walks                                                                                                               |

| 220 |   | 8.6  | TLB maintenance                                                                                                                              |

| 221 |   |      | 8.6.1 Recovering coherence                                                                                                                   |

| 222 |   |      | 8.6.2 Thread-local ordering and TLBI                                                                                                         |

| 223 |   |      | 8.6.3 Broadcast                                                                                                                              |

| 224 |   |      | 8.6.4 Virtualization                                                                                                                         |

| 225 |   |      | 8.6.5 Break-before-make                                                                                                                      |

| 226 |   |      | 8.6.6 Access permissions                                                                                                                     |

| 227 |   | 8.7  | Context synchronisation                                                                                                                      |

| 228 |   |      | 8.7.1 Relaxed system registers                                                                                                               |

| 229 |   | 8.8  | Problems                                                                                                                                     |

| 230 |   |      | 8.8.1 Reachability                                                                                                                           |

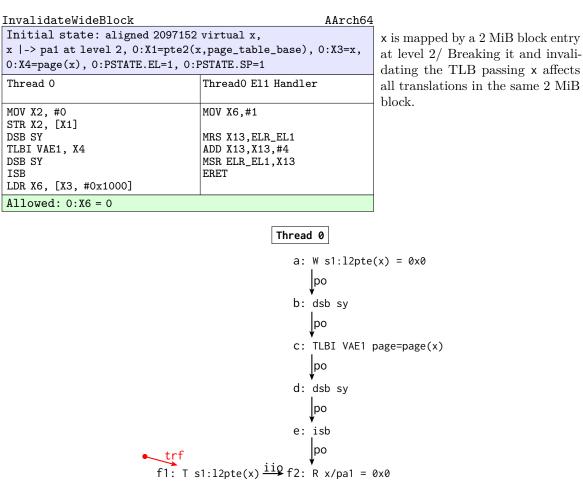

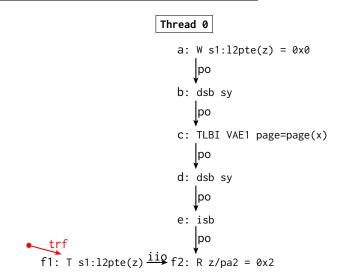

| 231 |   |      | 8.8.2 Wide invalidations $\dots \dots \dots$ |

| 232 |   | 8.9  | Contributions                                                                                                                                |

| 233 |   | 8.10 | Related work                                                                                                                                 |

|     | ~ |      |                                                                                                                                              |

| 234 | 9 |      | axiomatic VMSA model 154                                                                                                                     |

| 235 |   | 9.1  | Extended candidate executions                                                                                                                |

| 236 |   |      | 9.1.1 Candidate events                                                                                                                       |

| 237 |   | 0.2  | 9.1.2 Candidate relations                                                                                                                    |

| 238 |   | 9.2  | Cat model                                                                                                                                    |

| 239 |   | 9.3  | Axioms                                                                                                                                       |

| 240 |   | 9.4  | Relations                                                                                                                                    |

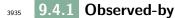

| 241 |   |      | 9.4.1 Observed-by                                                                                                                            |

| 242 |   |      | 9.4.2 Dependency-ordered-before                                                                                                              |

| 243 |   |      | 9.4.3 Barrier-ordered-before 162                                                                                                             |

| 244 |       | 9.4.4    | Translation-ordered-before                         | 162        |

|-----|-------|----------|----------------------------------------------------|------------|

| 245 |       | 9.4.5    |                                                    | 163        |

| 246 |       | 9.4.6    |                                                    | 164        |

|     |       | 9.4.7    |                                                    | 164        |

| 247 |       | 5.4.1    |                                                    | .04        |

| 248 | 10 Va | lidating | the RVM model 1                                    | 69         |

| 249 |       |          |                                                    | 169        |

|     | 10.   |          |                                                    | 169        |

| 250 |       |          |                                                    | 169        |

| 251 | 10    |          |                                                    | 109<br>170 |

| 252 | 10.   |          |                                                    |            |

| 253 |       |          |                                                    | 170        |

| 254 |       |          |                                                    | 171        |

| 255 | 10.   | 3 Valida | tion by abstraction                                | 173        |

|     |       |          |                                                    |            |

| 056 | III   | Excen    | tions and interrupts 1                             | 76         |

| 256 |       | Цлеер    |                                                    | 10         |

| 257 | 11 Re | elaxed p | recise exceptions 1                                | 77         |

| 258 | 11.   | 1 Introd | uction                                             | 178        |

| 259 |       | 11.1.1   | Exception taxonomy                                 | 178        |

| 260 |       |          |                                                    | 179        |

| 261 |       |          |                                                    | 179        |

| 262 |       |          |                                                    | 180        |

| 262 | 11    |          |                                                    | 180        |

|     | 11.   |          |                                                    | 180        |

| 264 |       |          |                                                    |            |

| 265 | 11    |          |                                                    | 181        |

| 266 | 11.   |          |                                                    | 182        |

| 267 |       |          | Out-of-order execution across exception boundaries |            |

| 268 |       |          | Context synchronisation and speculation            |            |

| 269 |       |          | Privilege level                                    |            |

| 270 |       |          | Dependency through system registers                |            |

| 271 |       | 11.3.5   | Ordering from asynchronous exceptions 1            | 186        |

| 272 |       | 11.3.6   | Exception-specific mechanisms                      | 186        |

| 273 |       |          | Exceptions and the intra-instruction semantics     |            |

| 274 |       |          | Disabling context synchronisation 1                |            |

| 275 | 11.   |          |                                                    | 187        |

| 276 |       |          |                                                    | 188        |

| 210 |       |          |                                                    |            |

| 277 |       |          |                                                    | 89         |

| 278 | 12.   | 1 Extend | ded candidates                                     | 189        |

| 279 | 12.   | 2 Extend | ded relations                                      | 191        |

| 280 | 12.   | 3 Challe | nges in defining precision                         | 191        |

| 281 | 12.   | 4 Scope  | and limitations                                    | 192        |

|     |       |          |                                                    |            |

| 282 |       |          |                                                    | 93         |

| 283 | 13.   | 1 Valida | ting against hardware                              | 193        |

| 284 | 13.   | 2 Execu  | table-as-a-test-oracle implementation 1            | 193        |

|     |       |          |                                                    |            |

| 285 | 14 Co | onclusio | n 1                                                | 96         |

| 286 |       | 1 Limita |                                                    | 196        |

| 287 |       |          |                                                    | 197        |

| -07 |       |          |                                                    |            |

| 288 |       |          |                                                    | 06         |

| 289 | A.:   |          | · · · · · · · · · · · · · · · · · · ·              | 206        |

| 290 | A.:   | 2 Guide  | to Instructions                                    | 208        |

| 291 |       | A.2.1    | Branches                                           | 208        |

| 292 |       | A.2.2    | Comparisons                                        | 211        |

| 293 |       | A.2.3    |                                                    | 211        |

| 294 |       |          | Memory accesses                                    | 213        |

| 295<br>296<br>297<br>298 |   | I<br>I | A.2.6<br>A.2.7 | Barriers                                                                                           | $\begin{array}{c} 215\\ 216 \end{array}$ |

|--------------------------|---|--------|----------------|----------------------------------------------------------------------------------------------------|------------------------------------------|

| 299                      | в | The (  | (i)Flat        | model                                                                                              | <b>218</b>                               |

| 300                      |   | Ē      | 3.0.1          | Intra-instruction Pseudocode Execution                                                             | 220                                      |

| 301                      |   | I      | 3.0.2          | Instruction Instance States                                                                        | 221                                      |

| 302                      |   | Ε      | 3.0.3          | Thread States                                                                                      | 222                                      |

| 303                      |   | Ε      | 3.0.4          | Model Transitions                                                                                  | 222                                      |

| 304                      |   | Ε      | 3.0.5          | Auxiliary Definitions                                                                              | 227                                      |

| 305                      |   | I      | 3.0.6          | Remarks about load/store exclusive instructions $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 227                                      |

| 306                      | С | Test f | forma          | t: system-litmus-harness                                                                           | 229                                      |

| 307                      | D | Proof  | f of vi        | rtual memory abstraction                                                                           | <b>231</b>                               |

| 308                      |   |        |                | ction                                                                                              | 231                                      |

| 309                      |   | D.2 A  | Anti-ab        | straction                                                                                          | 231                                      |

## Chapter 1

## Introduction

The computers we use every day are complex machines, made of many components, all working together to 312 execute the software we run on them. These machines act as interpreters for a custom binary programming 313 language, with commands made up of the instructions of the underlying architecture. These architectures 314 can be thought of as abstractions of the underlying hardware: programming languages whose syntax 315 is defined by the binary encoding of the instructions from the ISA (Instruction Set Architecture), and 316 semantics is the composition of the sequential behaviours of the instructions from the ISA, with the whole 317 machine execution model. The architecture therefore can be thought of as the *interface* between hardware 318 and software: defining the guarantees hardware must give and that software may rely upon. 319

Over the years much work has gone into defining, mathematically and precisely, the architectures that 320 the processors we use every day implement. This previous work covers Intel/AMD's x86 [1, 2, 3, 4], 321 Arm's ARMv7-A [5] and Armv8-A [6, 7] architectures, IBM's Power [8], RISC-V [9], and others. In 322 theory, this interface is straightforward to define. One can give precise formal semantics to the individual 323 instructions, as Arm does with its Architecture Specification Language (or ASL for short) [10, 11], and 324 then tie instructions together in a fetch-decode-execute loop. In practice, however, modern industrial 325 architectures accumulate great complexity and subtlety. The Armv8-A and Intel reference manuals have 326 11,500 [12], and 4922 [1] pages respectively, covering everything from the individual instructions to the 327 interactions between those instructions and the way they interact with memory. 328

The complexity of these interfaces becomes most apparent with the interaction with *multiprocessor* systems 329 [13]. When multiple processors are executing concurrently, and communicating through shared memory, 330 then various hardware optimisations, which are usually invisible to the programmer outside of timing 331 effects, can become *architecturally visible*, affecting the semantics of the machine code, that is the values 332 capable of being read or written to registers or memory by those processors. Over the years, these effects 333 have been studied as part of the field of 'relaxed memory' research, resulting in numerous formal models 334 for a variety of microprocessor architectures giving precise mathematical semantics to the concurrent 335 behaviours of 'userland' machine code programs [14, 15, 3, 4, 16, 7, 17]. Analogously for high-level 336 languages, there is similar work in understanding their relaxed memory behaviours which arise from 337 both their compilation to such low-level machine programs, and also from the compiler's optimisations 338 [18, 19, 20, 16].339

We now seek to expand this work on relaxed memory for the Arm architecture, to cover not just those 340 parts of the architectures used by userland processes, but the features required by systems software to 341 function. In this work we will focus on the Armv8-A architecture: the application-class processors that 342 power a large proportion of modern mobile devices. There are a few reasons to focus on Arm: (1) they 343 are ubiquitous and millions (perhaps even billions, with over a trillion devices running Arm hardware 344 today) of people rely on software running on Arm hardware every day, (2) Arm has a diverse ecosystem of 345 implementations, meaning software must program to this abstract interface much more tightly than one 346 might for other architectures, and (3) Arm have put a large amount of effort into precisely and formally 347 defining their ISA in their ASL language, enabling us to give a faithful specification to the architectural 348 envelope. 349

<sup>350</sup> Specifically, we will focus on key architectural features required by operating systems and hypervisors,

which are not accessible, or only partially accessible, to userland processes: instruction fetching and cache maintenance, virtual memory and TLB maintenance, and exceptions.

310

311

### **1.1** Arm-A architecture overview

In this work we will primarily be focused on Arm. Arm will serve as an example of representative modern

microprocessor architecture, and while the focus will be on Arm many of the behaviours and conclusions

will also apply to other architectures including RISC-V, IBM Power, and x86.

Arm produce three major classes of architectures, A-class (Application), R-class (Real-time) and M-class (Microprocessor). Arm predominantly produce *architecture*, and while they do design a small number of implementations it is primarily their partners who design and print their own. This will give us a large surface of interesting designs of the same architecture to test. In particular, we will focus on the

$_{361}$  A (Application)-class processors.

Arm's A-class architecture is intended to support general-purpose high-performance microprocessors, such as those found in mobile devices, tablets, laptops, and servers. Arm has three A-class architectures which can currently be found in modern hardware: ARMv7-A, Armv8-A, and Armv9-A. ARMv7-A is 32-bit only. Armv8-A and Armv9-A have 32-bit and 64-bit execution modes. Armv8-A and Armv9-A's 64-bit modes use the same base ISA and execution modes, except where Armv9 has some additional features, or required extensions, or bugfixes. We will focus here on the 64-bit architecture found in Armv8-A and

Armv9-A, and will use the term Arm-A to refer to both Armv8-A and Armv9-A interchangeably.

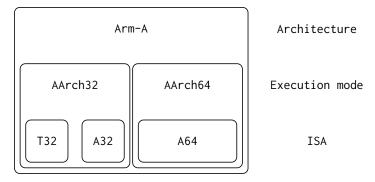

Execution of an Arm-A processor is split into two modes: AArch64 (for 64-bit execution) or AArch32 (for

370 32-bit execution). AArch64 mode uses the A64 instruction set. AArch32 mode can use either the T32 or

A32 instruction sets. This is illustrated in Figure 1.1.

Figure 1.1: Arm-A structure.

<sup>372</sup> A64, currently, has 402 'base' instructions and another 1,205 vector, matrix and floating-point instructions.

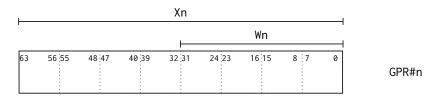

$_{373}$  It has 31 general-purpose registers, accessible through either 32-bit views as w0-w30, or as 64-bit views as

x0-x30, as shown in Figure 1.2. It has a dedicated zero register (wzr/xzr), and stack pointer register (sp). Instructions are fixed-width, with 32-bit opcodes, and in the typical RISC style: with most instructions

reading operands from registers, and writing results back to registers, with only limited support for

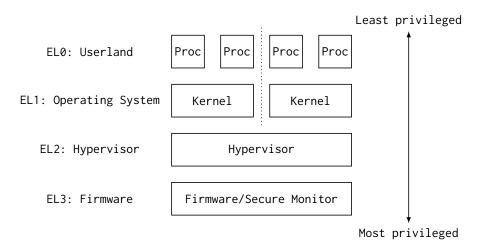

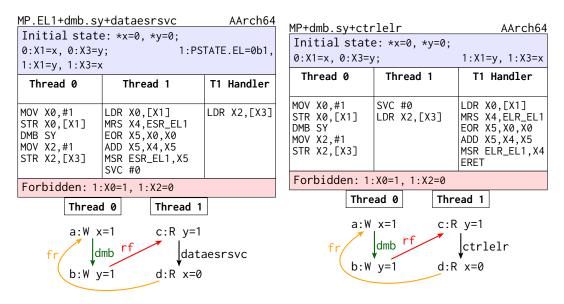

<sup>377</sup> immediate values. Execution in AArch64 is split into 4 'exception levels', these demark the levels of

<sup>378</sup> privilege that a process may have, ranging from EL0 (least privileged) to EL3 (most privileged). Typically

*userland* processes execute at EL0, with very limited access to hardware features; with operating systems

running at EL1, hypervisors running at EL2, and any firmware and secure monitor running at EL3.

<sup>381</sup> There are also secure modes, which we do not consider here. Each CPU has its own bank of registers; is

executing in either AArch64 or AArch32 execution mode; is fetching, decoding and executing instructions

from either the A64, A32 or T32 ISAs; is executing at at one of EL0, EL1, EL2 or EL3.

Figure 1.2: Arm-A W and X register views for a general-purpose register.

Figure 1.3: Arm-A exception levels.

## **1.2** Systems software

The programs we interact with on a day-to-day basis on our computers, our word processors and internet 385 browsers, are typically unprivileged programs, with restricted access to hardware. Such programs are 386 often referred to as executing in *userland*. These userland programs make up the bulk of the applications 387 we use every day, from spreadsheets, to web browsers, text editors, and so on. They typically execute with 388 the least privilege (in Arm, this means at ELO, as in Figure 1.3), and with the operating systems and 389 hypervisors below them restricting the access to memory they have through the use of virtual memory 390 (see Chapter 7). 391

Operating systems typically split userland execution into *processes*: discrete instances of programs, each 392 with some associated dedicated (virtual) memory [21, p. 85]. It is then the operating system, executing 393 with more privilege (at EL1), that configures and schedules these processes. 394

Modern operating systems seek to enforce isolation between these processes primarily through the 395 application of a virtual memory abstraction [21, pp. 185,194,604][22, p 227] (described in detail in Part II), 396 with each process behaving as if it had direct access to memory, when in fact the operating system (via 397 the hardware supporting it) are redirecting the accesses at runtime. 398

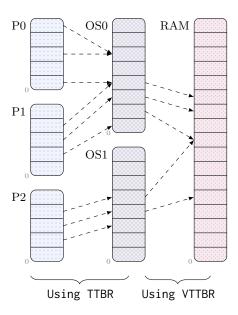

This virtual memory abstraction can be layered, with an extra level of abstraction below the operating 399 systems controlled by a hypervisor. Hypervisors behave similarly, but instead of controlling many processes 400 at EL0 they instead can control multiple operating systems at EL1. 401

Finally, software at EL3 executes any firmware or secure monitor. Generally, the firmware performs 402 hardware-specific actions, especially during boot (reading and writing implementation-defined configuration 403 registers and performing any functionality required by the System-on-Chip). The Secure Monitor is a 404

part of the Arm architecture's TrustZone security extensions, and we will not discuss these features here. 405

Figure 1.3 demonstrates a typical setup, with firmware running at EL3, a hypervisor at EL2, which is 406 controlling a couple of operating systems, each of which has multiple processes under its control.

407

### **1.3 Relaxed memory**

The implementations of programming languages, in the form of compilers and interpreters either in software or hardware, are not just direct implementations of the simple in-order sequential semantics one might expect. Instead, as time progressed these implementations have acquired multiple layers of abstraction, made with increasing complexity. Compilers and hardware re-write programs to be faster, use less space, and be more compact. They propagate and duplicate reads, subsume or outright eliminate writes, reorder operations in the program, replace one computation with another, or even just remove entire sections of the program entirely.

These optimisations may be *semantics preserving* with respect to the simple sequential semantics: aside from the timing effects they are designed to cause they are invisible to the programmer. This is, however, not true in all cases, with many highly desirable optimisations not preserving the source program's semantics [23].

It is multithreaded programs, and multicore processors, which often breaks the assumptions made by these 420 optimisations. As an example, take Intel's x86 microprocessor architecture. It allows its implementations 421 to perform an innocuous-sounding optimisation: to buffer writes together locally. This store buffering 422 optimisation is ubiquitous in the hardware world, but it permits multiple cores to have mutually inconsistent 423 views of memory [23, 3, 4]; where, at the same point in time, different cores see different values for the 424 same memory address. If the programmer was unaware of these behaviours and the required mitigation 425 in software, then this could break key invariants of software, leading to critical bugs in synchronisation 426 primitives [23], data structures, or software more generally [24]. 427

Intel, and their x86 architecture, is not the only example of hardware architectures performing such 428 optimisations, and store buffering is not the only behaviour hardware exhibits. Arm [12], RISC-V [25], 429 and IBM's Power [26] architectures all exhibit their own behaviours, with consequential requirements on 430 software. Each of these microprocessor architectures comes with its own reference manual, comprised of 431 thousands, or tens of thousands, of pages with a mix of prose and pseudocode, attempting to describe 432 these behaviours. These architectures are incomparable, the behaviours they allow are not subsets 433 of one another. Instead, there are several optimisations that some architectures allow as observable 434 behaviour, where others do not. Those optimisations include, but are not limited to, things such as: 435 reordering of instructions, prefetching and caching of data and instructions, buffering of loads and stores, 436 hierarchical cache layouts, and branch prediction with speculation down those branches. It is not that 437 some implementations perform these optimisations while others do not, but that those architectures which 438 allow such behaviours to be observed do not require that the hardware include relevant hazard checking 439 or invalidations which would recover from 'bad' states. 440

It is not just hardware that has these concerns. A variety of software languages, including C and C++

[27, 28], Java [29, §17.4], Rust [30], and Haskell [31], are all known to have comparable behaviours, derived

both from similar optimisations done by their compilers and interpreters, but also inherited from the

hardware they run upon.

Over the decades, the community has spent a large amount of effort in understanding the behaviours the hardware actually exhibits, by empirically observing what extant hardware does, by talking with architects and hardware designers about what they imagine hardware could do, now or in the future, and by building precise mathematical models which capture the architectural 'envelope' of allowable behaviours. These models come in many flavours, and in Chapter 2 we will explore two such models for Arm, and the set of behaviours they are intended to capture.

## 451 **1.4 Contributions**

<sup>452</sup> In this work, we extend the previous relaxed memory work on Arm into the realm of systems software: <sup>453</sup> instruction fetch and cache maintenance (Part I), pagetables and TLB maintenance (Part II), and a <sup>454</sup> start on exception handling (Part III). We will produce both axiomatic-style declarative semantics and <sup>455</sup> microarchitectural-style operational semantics to cover a variety of those parts of the architecture.

### 456 1.4.1 Artifacts

457 This work will present:

- A set of litmus tests for instruction fetching and cache maintenance (Ch. 3), covering many areas

and features and clarifying the architectural intent in those areas.

- <sup>460</sup> ▷ A microarchitectural-style structural-operational-semantics for Arm-A (Ch. 4), covering ifetch and <sup>461</sup> cache maintenance, as an extension to the existing Flat model.

- An equivalent formulation as an axiomatic-style declarative semantics (Ch. 5), as an extension to

the herd-style Armv8 axiomatic model.

- An extension of the litmus7 tool, and a set of results from testing against a range of hardware (Ch. 6).

- A set of litmus tests for virtual memory and TLB maintenance, using the whole Arm translation

table walk with both stages (Ch. 8).

- An axiomatic-style declarative semantics (Ch. 9) as an extension to the original Armv8 model.

- $\wedge$  A new hardware testing harness, and validation of the models by experimentation against hardware,

- $_{470}$  and through abstraction proofs (Ch. 10).

- $_{471}$   $\triangleright$  A set of litmus tests for precise exceptions in Arm (Ch. 11).

- $\wedge$  An axiomatic-style declarative semantics for precise exceptions in Arm (Ch. 12).

- An extension to the hardware testing harness of Chapter 10 to support hardware testing of exceptions,

- and validation of the previously mentioned precise exceptions semantics on hardware (Ch. 13).

## 475 **1.5** Publications and collaborations

The work presented in Chapters 3 to 13 were done in collaboration with a variety of other people on different aspects, and resulted in the production of the following publications:

- <sup>478</sup> b 'ARMv8-A system semantics: instruction fetch in relaxed architectures', in the Proceedings of the 29th European Symposium on Programming (ESOP 2020), by Ben Simner, Shaked Flur, Christopher Pulte, Alasdair Armstrong, Jean Pichon-Pharabod, Luc Maranget, and Peter Sewell

<sup>480</sup> [32].

- <sup>482</sup> b 'Isla: Integrating full-scale ISA semantics, axiomatic concurrency models', in the Proceed <sup>483</sup> ings of the 33rd International Conference on Computer Aided Verification (CAV 2021), by Alasdair

<sup>484</sup> Armstrong, Brian Campbell, Ben Simner, Christopher Pulte, and Peter Sewell [33].

- <sup>485</sup> (Relaxed virtual memory in Armv8-A', in the Proceedings of the 31st European Symposium

on Programming (ESOP 2022), by Ben Simner, Alasdair Armstrong, Jean Pichon-Pharabod,

<sup>487</sup> Christopher Pulte, Richard Grisenthwaite, and Peter Sewell [34].

- <sup>488</sup> b 'Precise exceptions in relaxed architectures (pre-publication)', in the unpublished work,

<sup>489</sup> by Ben Simner, Alasdair Armstrong, Thomas Bauereiss, Brian Campbell, Ohad Kammar, Jean

<sup>490</sup> Pichon-Pharabod, and Peter Sewell [35].

- <sup>491</sup> b 'Isla: Integrating full-scale ISA semantics, axiomatic concurrency models (extended version)', in the Formal Methods in System Design (May, 2023), by Alasdair Armstrong, Brian Campbell, Ben Simner, Christopher Pulte, and Peter Sewell [36].

Many of the aspects of the work presented in this thesis were done jointly with many of the people listed 494 above. The Isla tooling was primarily written by Alasdair Armstrong. The work on the litmus and 495 diy tools was done by Luc Maranget. The production of litmus tests and discussions with architects 496 and microarchitects was done jointly with Shaked Flur, Christopher Pulte, Ohad Kammar, Thibaut 497 Pérami, Jean-Pichon Pharabod, and Peter Sewell. The writing of models was done in collaboration with 498 Christopher Pulte and Shaked Flur (for ifetch); Christopher Pulte and Thibaut Pérami (for VMSA); and 499 Jean Pichon-Pharabod and Ohad Kammar (for exceptions). Validation of the models, through proof and 500 hardware testing, was done jointly with Jean Pichon-Pharabod (on the VMSA abstraction proofs) and 501 Luc Maranget (test generation and hardware testing for ifetch). 502

Much of the above work was done in collaboration with Arm and their staff, in particular their chief 503 architect, Richard Grisenthwaite. He is our primary contact within Arm, and we have a close collaboration with him characterised by discussions on Arm hardware, the requirements of the software that runs on 505 them, the consequences of the models we propose, and, where relevant, the history of the architecture. 506 In cases where we present some behaviour and declare that it is 'allowed by Arm', it usually means 507 we have confirmation from the chief architect directly. However, it is not just the chief architect we 508 collaborate with, but many members of Arm's staff: Will Deacon, and later Jade Alglave, as the primary 509 maintainer of the Arm memory models; and Ian Caulfield, Nikos Nikoleris, Gustavo Petri, Anthony Fox, 510 Martin Weidmann, and others, who discussed Arm modelling efforts, Arm hardware implementations, 511 and provided feedback individually on many of the aforementioned publications. 512

## 513 **1.6 Overview**

- <sup>514</sup> This document is split into five main parts:

- > Introduction and background (Chapters 1 and 2)

- > Instruction fetch (Part I comprising chapters 3-6)

- <sup>517</sup> ▷ Virtual memory (Part II comprising chapters 7-10)

- <sup>518</sup> ▷ Exceptions (Part III, comprising chapters 11-13)

- <sup>519</sup> ▷ Limitations and Conclusion (Chapter 14)

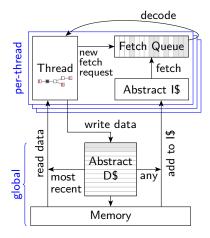

Background Chapter 2 covers the fundamental concepts behind relaxed memory. the idea of litmus testing as a means to clarify and understand architecture, including a selection of important and useful litmus tests from the literature; how Arm defines their intra-instruction semantics and how such semantics compose with a concurrency model; the two kinds of concurrency models we will explore in this thesis, microarchitectural-style operational semantics and axiomatic-style declarative semantics; and describe instantiations of these for Arm-A.

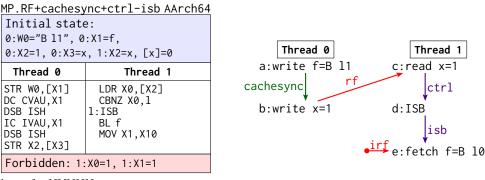

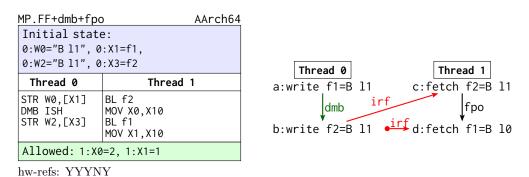

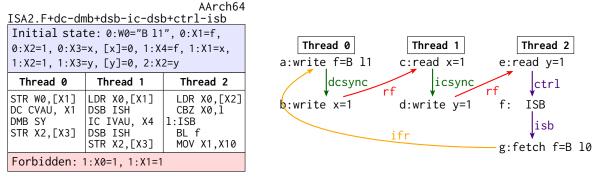

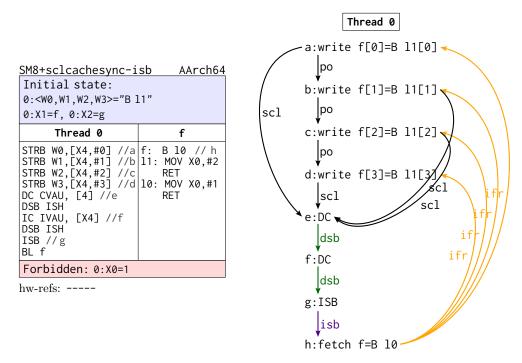

**Part I: Instruction fetching** We start with a brief overview of the existing prose text for instruction fetch 526 and the related instruction (and data) cache maintenance operations. Focusing primarily on self-modifying 527 (and concurrent modification) of code, such as what is required for JITs, dynamic loaders, and operating 528 systems schedulers, we produce a set of litmus tests (Ch. 3) to capture the key relaxed behaviours that 529 arise from the optimisations found in modern microprocessors, and clarify where such behaviours were 530 unclear. We produce a microarchitectural-style operational semantics (Ch. 4) based on our discussions 531 with architects and micro-architects. We then produce an axiomatic model (Ch. 5) intended equivalent 532 to the operational model. We then validate that these models (Ch. 6), confirming they coincide for the 533 litmus tests given in the chapter. We automatically generate a large test suite of novel tests and check 534 the two models do not diverge on these tests. We additionally check that they do not forbid behaviours 535 exhibited on hardware by running the test suite on a selection of modern Arm processors. 536

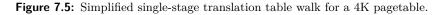

**Part II: Virtual memory** Structured similarly to the instruction-fetching chapters, but independently of 537 them, we explore the Arm Virtual Memory Systems Architecture or VMSA. We begin with an overview of 538 the sequential aspects (Ch. 7), describing the structure and behaviour of the Arm address translation 539 and memory management architecture without considering concurrency or caching effects. Then, we 540 explore the relaxed behaviours of virtual memory (Ch. 8) by producing litmus tests and discussing the 541 architectural intent. We produce an axiomatic-style model for relaxed virtual memory (Ch. 9), as an 542 extension to the original (user mode) model, using the whole Arm translation table walk, including 543 multiple stages, and TLB maintenance. Finally, there is a discussion on the validation of this model 544 (Ch. 10) achieved by discussion with the Arm chief architect, along with some limited testing of current 545 Arm hardware, and some proofs over the axiomatic model for some expected key abstraction results. 546

Part III: Exceptions A short overview of the in-progress work on relaxed exceptions in Arm-A. We begin with a discussion on the Arm interpretation of precise exceptions, before producing some key litmus tests, an axiomatic model, and finally produce some preliminary hardware results to support the models.

<sup>550</sup> **Conclusion** Finally, Chapter 14 presents a short summary of the presented work, its limitations, and

relation to other work in the area. We discuss what was learned, in terms not only of the models produced but also of the process itself, before finally touching on what remains as potential future work.

Chapter 2

## Modelling Arm: background

Now we turn our attention to the current well-established methods of precisely and formally modelling relaxed memory behaviours, in the context of Arm-A. In this chapter, we will cover two methods: microarchitectural-style operational semantics, which mimic the mechanisms seen on hardware; and axiomatic-style declarative models which succinctly define the validity of whole-program executions.

<sup>559</sup> We shall see that the idea of *litmus testing* is central: litmus tests provide a way of succinctly and efficiently

4560 describing and enumerating the behaviours of the underlying architecture that the models should allow or

<sup>561</sup> forbid. We will start by looking at litmus testing in general, and some specific litmus tests of interest to

the Armv8-A models, before looking at the models in detail.

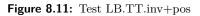

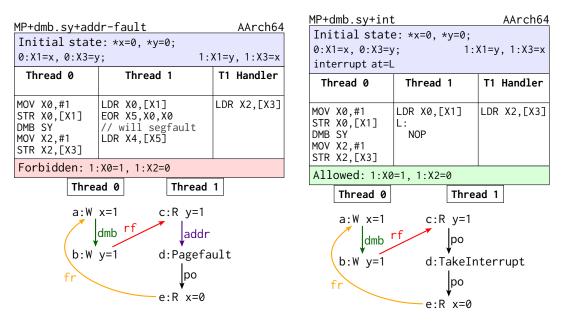

### 2.1 Relaxed behaviours and litmus testing

The foundation of much of the relaxed memory work has been focused on *litmus tests*, small, self-contained, executable, snippets of code. They each capture a simple pattern or shape one may find in software.

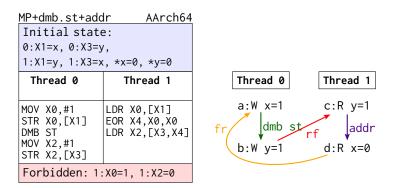

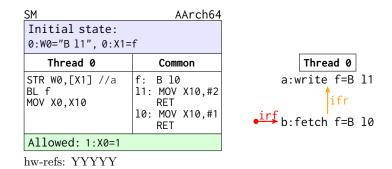

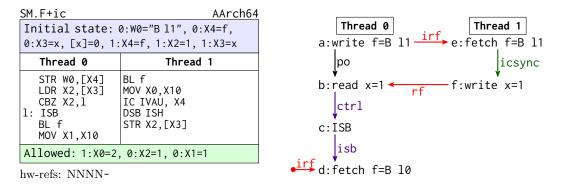

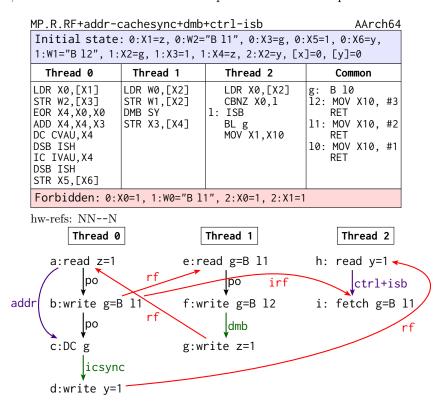

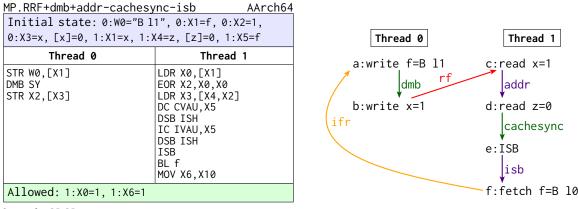

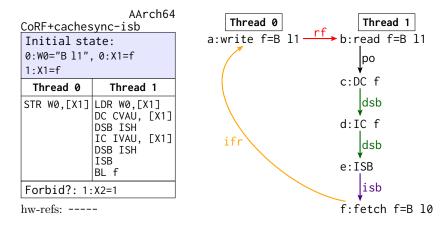

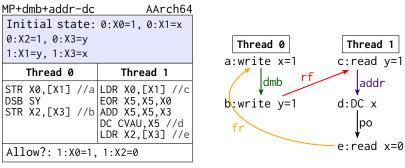

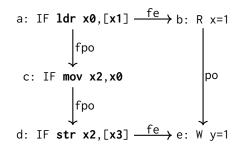

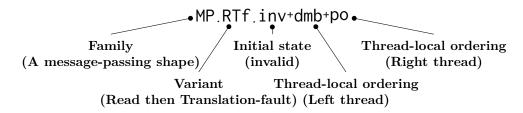

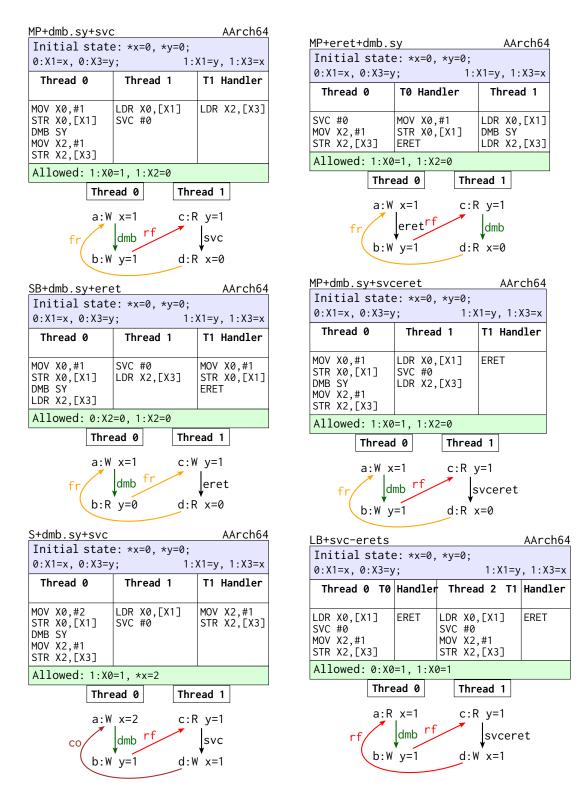

Take the classic MP ('Message passing') litmus test as an example [23]. The code listing for the AArch64 566 (Arm-A) variant can be found in Figure 2.1. The 'MP' portion of the name captures the shape: the core 567 pattern (or precisely, the cycle) of events which act as the skeleton of the test. In this case, message 568 passing is a common software pattern where one thread writes some data followed by a flag signalling 569 the data is ready, while another thread concurrently reads the flag in order to further read the data. 570 Thus, the 'MP' shape implies a two-threaded test with two locations (typically named x and y), with one 571 thread (typically written first) writing to the locations, and another thread reading them in the converse 572 order. The second half of the name ('+pos') designates the variation on the shape, in this case, that 573 both threads have accesses just program-order after each other with no other barriers or dependencies. 574 Typically these variations are defined as the sequence of orderings between events (separated by - in the 575 name) for each thread (separated by +). Thus, we get a whole *family* of litmus tests based on the basic 576 MP shape: MP+pos (the one shown here), MP+dmbs (with an Arm dmb memory barrier on each thread), 577 MP+dmb.st+addr (with an Arm dmb.st memory barrier on the writer thread and an address dependency 578

579 on the reader thread), and so on.

553

554

| MP+pos                | AArch64     |  |  |  |  |  |

|-----------------------|-------------|--|--|--|--|--|

| Initial state:        |             |  |  |  |  |  |

| 0:X1=x, 0:X3=y,       |             |  |  |  |  |  |

| 1:X1=y, 1:X3=x, *x=0, |             |  |  |  |  |  |

| *y=0                  |             |  |  |  |  |  |

| Thread 0              | Thread 1    |  |  |  |  |  |

|                       |             |  |  |  |  |  |

| MOV X0,#1             | LDR X0,[X1] |  |  |  |  |  |

| STR X0,[X1]           | LDR X2,[X3] |  |  |  |  |  |

| MOV X2,#1             | ,           |  |  |  |  |  |

| STR X2,[X3]           |             |  |  |  |  |  |

| Allowed: 1:X0         | )=1, 1:X2=0 |  |  |  |  |  |

Figure 2.1: MP test code listing.

The code listing given is totally standard [37]: the top line contains the name of the litmus test (MP+pos),

and the architecture that this variant is for (AArch64); the second section contains the initial register and memory state; the next section contains the assembly code listing for each thread; and finally at the

<sup>582</sup> bottom is a conjectured outcome (plus its architectural intent, if known) given as a constraint on the final

register and memory state. On Arm, the outcome given in the listing in Figure 2.1 is allowed.

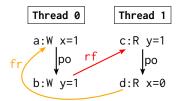

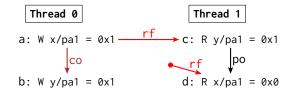

On a sequentially consistent (SC) machine, whose executions are simply the interleaving of the instructions 585 of all threads [38], there are many executions of the listed code, each giving rise to (potentially distinct) 586 final states. To see the highlighted outcome, where Thread 1 reads 1 for y but 0 for x, there is only one 587 possible combination of reads: that the read of y reads from the write to y, and the read of x reads from 588 the initial memory state. This combination is not consistent with any of the simple interleavings of the 589 instructions a sequentially consistent machine would perform. We represent these executions not as an 590 interleaving of the instructions, but as a graph of the events of those instructions (the reads and writes 591 they perform) connected by their implicit orderings. There may be, and in this case, are, multiple different 592 operational traces that lead to the same execution witness, which we shall explore later. The execution 593 graph that corresponds to the allowed outcome can be found in Figure 2.2. 594

Figure 2.2: MP test execution diagram.

The nodes on the left, below the Thread 0 label, correspond to events from executing Thread 0 of the 595 program. The event labelled a corresponds to the propagation of the first store in Thread 0 (the write 596 of 1 to x) to memory, and event b corresponds to the write of the second store being propagated. They 597 are related by program-order (po) indicating that the instruction a came from is earlier than that of b 598 in the instruction stream of the processor; that is, a comes before b in the control flow of that thread, 599 as determined by the order the processor fetched and decoded the instructions in. Similarly, below the 600 Thread 1 label we see the event labelled c: the read event corresponding to the first load, reading the 601 address y and getting the value 1. The value read came from the write event b, therefore b is related to c 602 603 by the reads-from (rf) relation. Finally, the load of x reads from the initial value in memory, so we have another read event, labelled d, which reads 0. The read d of x read a value from a write to x from before 604 the event a happened, in this case that is the initial memory from the 'Initial state' of the test, and so d 605 is related to a by the from-reads (fr) relation. 606

On Arm, the writes and reads need not execute in the order they appear in the program. So, while this execution appears to have a cyclic dependency in the order events must have happened in, the cycle can be broken by re-ordering the execution of either the reads or writes. The execution is therefore allowed, and we readily observe this outcome on most modern hardware.

**Litmus testing** We use litmus tests to explore *behaviours*: particular patterns in code, or specific 611 hardware mechanisms that are responsible for allowing or forbidding the test. Many litmus tests exercise 612 many microarchitectural mechanisms whose composition or confluence leads to the final result, or where 613 there may be multiple different mechanisms or choices that could each independently lead to the same 614 result. For example, in the MP+pos test we just saw, there are three well-understood microarchitectural 615 explanations: that the stores are committed out-of-order (re-ordered within the pipeline, store queue, or 616 other thread-local storage), that the stores propagate out-of-order (are pushed out-of-order into the shared 617 memory), or that the loads satisfy out-of-order (either requested out-of-order in the pipeline, or requests 618 returned out-of-order from the memory subsystem). Any of the above explanations are alone sufficient to 619 allow the relaxed outcome highlighted by the test. One needs to prevent out-of-order execution on both 620 sides of the test (through the use of memory barriers, for example) to forbid that relaxed outcome. 621

Previous work has systematically enumerated these various patterns to produce a large collection of litmus 622 tests, for a range of architectures, each with an assortment of variations for different intra-thread orderings 623 (for barriers, dependencies, and so on). This has included obtaining both the architectural intent for 624 those patterns, as well as extensive testing campaigns on a variety of modern hardware. In some cases, 625 some outcome may be *architecturally allowed*, that is, the final state constraint is permitted to occur in 626 practice, but has not been experimentally observed on any hardware so far. In other cases, there may 627 be no architecturally allowed execution that permits a particular outcome, but it is still observed on 628 hardware: these are (or at least imply there exists) hardware errata, more commonly referred to as 'bugs'. 629 We will not do an exhaustive review of all the behaviours that are allowed and forbidden in Arm, instead 630 referring the reader to the existing literature [14, 37, 39, 16, 7, 6, 40]. However, we will briefly look at 631 some of the behaviours that the reader should be familiar with in order to understand future chapters, 632 namely coherence, barriers and dependencies, and multi-copy atomicity. 633

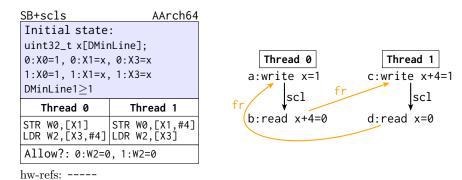

### 634 2.1.1 Thread-local ordering

On Arm, instructions need not execute in the order they appear in the program, as we just saw. Reads and writes are free to be re-ordered with respect to each other, with few restrictions. This is in contrast to other architectures such as Intel/AMD's x86, where only writes can be re-ordered with respect to program-order later reads (through store buffering) [1, 23, 3]. Note that this does not mean that the hardware is not allowed to re-order the instructions, but that if it does it must preserve the illusion of in-order execution to the programmer.

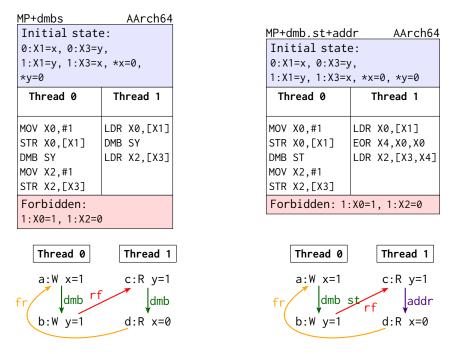

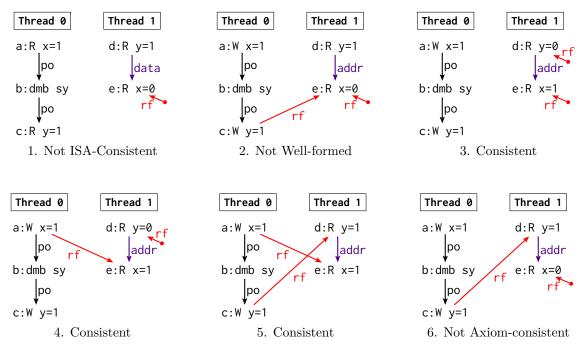

<sup>641</sup> Not all re-orderings are permissible; Arm requires that single-threaded programs should behave as if <sup>642</sup> executed sequentially, at least for loads and stores. This means that non-SC executions only come about <sup>643</sup> through the interaction between multiple threads. We have already seen this with the MP test earlier. To <sup>644</sup> forbid the outcome of that test we must add barriers or dependencies to enforce thread-local ordering, <sup>645</sup> preventing the events from being reordered. Two (forbidden) variations of MP can be found in Figure 2.3.

Dependencies in Arm arise from the intrinsic control and data flow of the program. Usually, they are 646 categorised into three kinds: address dependencies (addr), from reads to memory events that use that 647 read in the computation of the address the memory event accesses; data dependencies (data), from reads 648 to writes, where the value read is used in the computation of the value written; and control dependencies 649 (ctrl), from reads to events of instructions program-order after a (conditional) branch in the program 650 where the value of the read was used in the computation of the value used in the condition. Note that these 651 are not purely dynamic properties of the execution, but rather they are syntactic in that the dependencies 652 an instruction induces is a statically known property, thus there are no so-called 'fake' dependencies: the 653 values read or written at runtime by an instruction does not matter only the set of registers it accesses. 654

Not all dependencies are equal. On Arm, address and data dependencies enforce both read-to-read and read-to-write ordering, control dependencies enforce read-to-write but not read-to-read ordering. Speculation allows reads to happen 'early', but not writes; this gives an asymmetry where control dependencies provide strength to a write but not a read. This can be seen in the two tests in Figure 2.4.

**Figure 2.3:** Two variants of MP with thread-local ordering. On the left: MP+dmbs with Arm DMB barrier between instructions. On the right: MP+dmb.st+addr with an address dependency between the reads.

| MP+dmb.st+ct                   | rl AArch64                      |   |                 |                                |

|--------------------------------|---------------------------------|---|-----------------|--------------------------------|

| Initial stat                   | e:                              |   | LB+ctrls        | AArch64                        |

| 0:X1=x, 0:X3=                  | y,                              |   | Initial state   | : 0:X1=x, 0:X3=y,              |

| 1:X1=y, 1:X3=>                 | x, *x=0, *y=0                   |   | 1:X1=y, 1:X3=x, | *x=0, *y=0                     |

| Thread 0                       | Thread 1                        |   | Thread 0        | Thread 1                       |

| MOV X0,#1                      | LDR X0,[X1]                     |   | LDR X0,[X1]     | LDR X0,[X1]                    |

| STR X0,[X1]                    | CBNZ X0,LC00                    |   | CBNZ X0,LC00    | CBNZ X0,LC01                   |

| DMB ST                         | LC00:                           |   | LC00:           | LC01:                          |

| MOV X2,#1                      | LDR X2,[X3]                     |   | MOV X2,#1       | MOV X2,#1                      |

| STR X2,[X3]                    |                                 |   | STR X2,[X3]     | STR X2,[X3]                    |

| Allowed: 1:X0                  | 0=1, 1:X2=0                     |   | Forbidden: 0:>  | (0=1, 1:X0=1                   |

| Thread 0                       | Thread 1                        | ] | Thread 0        | Thread 1                       |

| a:W x=1<br>fr dmb s<br>b:W y=1 | c:R y=1<br>trf ↓ctrl<br>d:R x=0 |   | a:R x=1         | c:R y=1<br>rf ↓ctrl<br>d:W x=1 |

| D.W y-1                        | U.R X-0                         |   | 5.W y-1         | U.W X-1                        |

Figure 2.4: Two litmus tests with speculation.

On the left: MP+dmb.st+ctrl with Arm  $\tt DMB$  barrier between the writes, but a control dependency between the reads.

On the right: LB+ctrls, a variant of the classic 'load buffering' litmus test, with control dependencies to both writes.

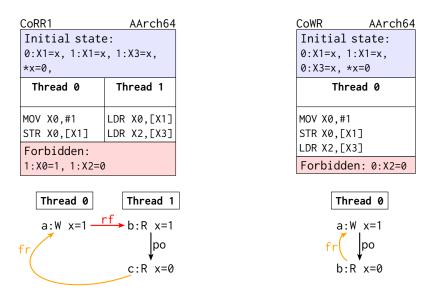

On the left: CoRR1, that two subsequent reads of the same location in the same thread should be consistent with the coherence order. On the right: CoWR, that a read of a location cannot skip over a newer program-order earlier write from the same thread.

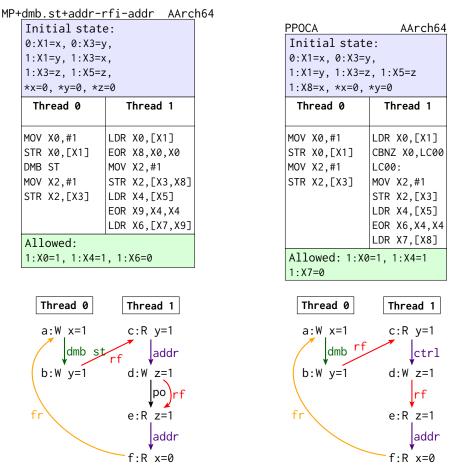

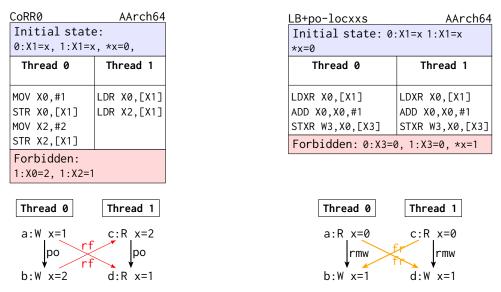

#### 659 2.1.2 Coherence

A guarantee provided by most modern microprocessor architectures is *coherence*: that there is for each location, a total order that writes to that location happen in, that all threads agree on [8]. Microarchitecturally, this emerges naturally from the desire to ensure that writes are never dropped by the cache protocol, and since writes may be of sub-cache-line size (down to individual bytes) the cache protocol must ensure consistency over whole cache lines at a time.

<sup>665</sup> This property is one that sets processor consistency models apart from those one would find in databases <sup>666</sup> and other distributed systems, which generally do not require it, such as the classic *causal consistency* <sup>666</sup> model for distributed systems [41]

<sup>667</sup> model for distributed systems [41].

$_{668}$  Two of the key litmus tests for coherence can be found in Figure 2.5.

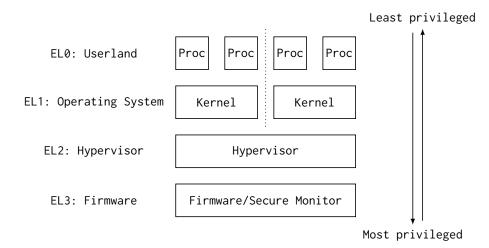

### 669 2.1.3 Multi-copy atomicity

<sup>670</sup> Coherence is not sufficient to guarantee that all threads agree on what the most recent write is at the same <sup>671</sup> point in time. Eventually, they will all have seen the same writes to the same location in the same order, <sup>672</sup> but at any particular moment, some threads may not have caught up to the latest write yet. Architectures <sup>673</sup> that have this property are called *non-multi-copy atomic* [13].

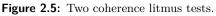

Arm has a kind of partial multi-copy atomicity, which they term other-multi-copy atomicity. Other-multi-674 copy atomicity gives guarantees similar to normal multi-copy-atomicity, but allows writes to be read by the 675 writing thread itself earlier than they can be seen by other threads, however, once a write has propagated 676 to another thread then all threads must see that write or something newer [7]. The hardware mechanism 677 which motivates this is *write forwarding*: the processor can satisfy a read from a same-thread same-location 678 program-order-earlier write, if that write has committed, even before the write has propagated out to 679 memory. Figure 2.6 contains the classic PPOCA (preserved-program-order-control-address) litmus test, 680 which shows that writes can be observed locally before being propagated to other threads, even down 681 speculative branches. Figure 2.7 shows the IRIW (independent-reads independent-writes) litmus test, 682 which demonstrates the latter point, that writes propagate to all threads simultaneously. 683

**Figure 2.6:** Two litmus tests with write forwarding. On the left: MP+dmb.st+addr-rfi-addr with write-forwarding down a non-speculative branch. On the right: PPOCA, with write-forwarding down a speculative branch.

| IRIW+dmbs                                         |                                                   |                          | AArch64                                           |  |  |  |  |  |

|---------------------------------------------------|---------------------------------------------------|--------------------------|---------------------------------------------------|--|--|--|--|--|

| <pre>Initial state: 0:X1=x, 1:X1=x, 1:X3=y,</pre> |                                                   |                          |                                                   |  |  |  |  |  |

| 2:X1=y, 3:X1=y, 3:X3=x, *x=0, *y=0                |                                                   |                          |                                                   |  |  |  |  |  |

| Thread 0                                          | Thread 1                                          | Thread 2                 | Thread 3                                          |  |  |  |  |  |

| MOV X0,#1<br>STR X0,[X1]                          | LDR X0,[X1]<br>MOV X2,#1<br>DMB SY<br>LDR X2,[X3] | MOV X0,#1<br>STR X0,[X1] | LDR X0,[X1]<br>MOV X2,#1<br>DMB SY<br>LDR X2,[X3] |  |  |  |  |  |

| Forbidden: 1:                                     | X0=1, 1:X2=0,                                     | 3:X0=1, 3:X2=0           |                                                   |  |  |  |  |  |

| Thread 0                                          | Thread 1                                          | Thread 2                 | Thread 3                                          |  |  |  |  |  |

| a:W x=1 <u>rf</u><br>fr                           | b:R x=1<br>dmb fr<br>c:R y=0                      | d:W y=1 <u>r</u> 1       | e:R y=1<br>dmb<br>f:R x=0                         |  |  |  |  |  |

Figure 2.7: IRIW+dmbs: a classic multi-copy atomicity litmus test.

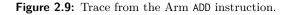

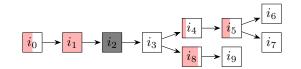

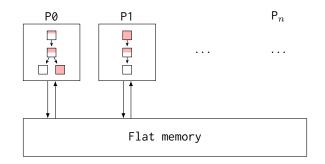

#### 2.2 Intra-instruction semantics 684

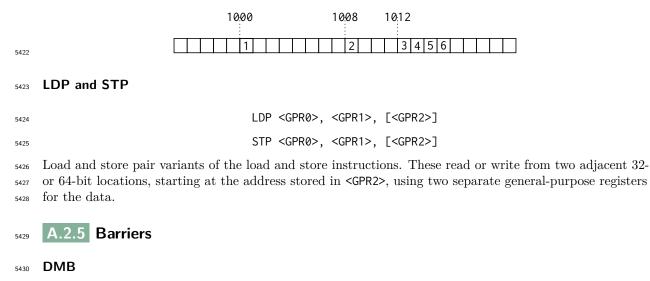

Much of the work in this document will be dedicated to understanding the *inter*-instruction and concurrency 685 aspects of the semantics. Previous work has, for Arm and RISC-V, established high-fidelity models for 686 the *intra*-instruction behaviour of individual instructions. That is, the sequential behaviour of the register 687 and memory accesses, and any arithmetic over them, the instruction performs. 688